# VIC REVEALED NICK HAMPSHIRE

# VIC\* REVEALED

NICK HAMPSHIRE

## First published in 1982 by Gerald Duckworth & Co. Ltd The Old Piano Factory 43 Gloucester Crescent, London NW1

© 1982 by Nick Hampshire

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, or otherwise, without the prior permission of the publisher.

ISBN 0-7156-1699-4

British Library Cataloguing in Publication Data Hampshire, Nick

1. Vic (Computer)

I. Title

001. 64'04 QA76.8.P47

ISBN 0-7156-1699-4

Typeset by Centrepoint Typesetters Ltd., London Printed in Great Britain by Redwood Burn Ltd., Trowbridge and bound by Pegasus Bookbinding, Melksham

### INTRODUCTION

This book is a collection of discoveries about the VIC, how and why it works, and how to use these facts to write better programs and perform more interesting functions. The book is divided into five sections, each section covering one of the principal functional blocks into which the basic VIC computer can be divided. The different aspects of the VIC dealt with in each section cover most of the advanced applications for which the VIC can be used.

The VIC is produced in several slightly different versions, in different parts of the world. This book is written for version 7 machines which are designed for use with European PAL TV sets. The US version 6 machines use the 6560 VIC chip which is compatible with the US 525 line TV. The Japanese version 1 machines use the 6560 and also have Japanese character keyboard and character generator. There are slight differences in the operating system software of these three versions but they do not affect most of the information in this book.

I should like to thank Commodore UK and Commodore US for their assistance in writing this book, in particular the following people: John Baxter and Malcolm North of CBM UK and Mike Tomczyk, Shiraz Shivji and Bob Russell of CBM US.

Nick Hampshire

# **CONTENTS**

| 1 — The 6502 Microprocessor        | - V           |

|------------------------------------|---------------|

| 2 — Vic System Software            | - 42          |

| 3 — The 6561 Video Interface Chip  | <b>– 11</b> 0 |

| 4 — The 6522 Via and the User Port | <b>–</b> 150  |

| 5 — Vic I/O Functions              | - 186         |

|                                    |               |

| APPEN | DIX #1 - CBM Codes    | 237 |

|-------|-----------------------|-----|

|       | # 2 $-$ Wedge Program | 243 |

|       | #3-6502 Inst.         | 253 |

|       | #4 - Hex-Dec          | 255 |

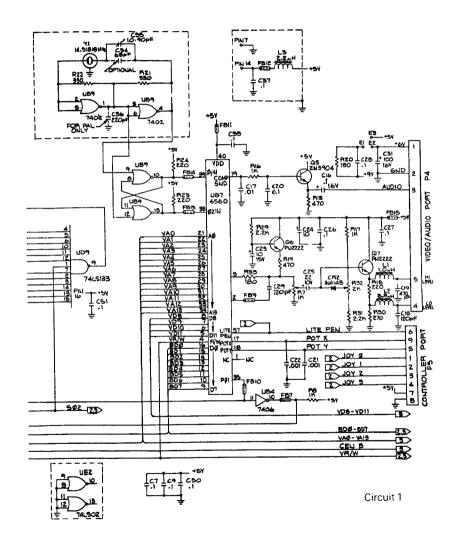

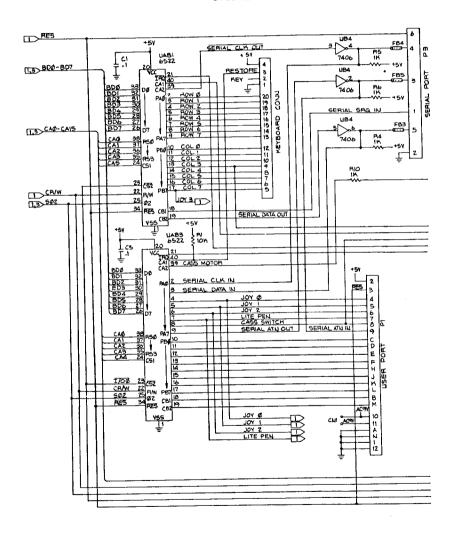

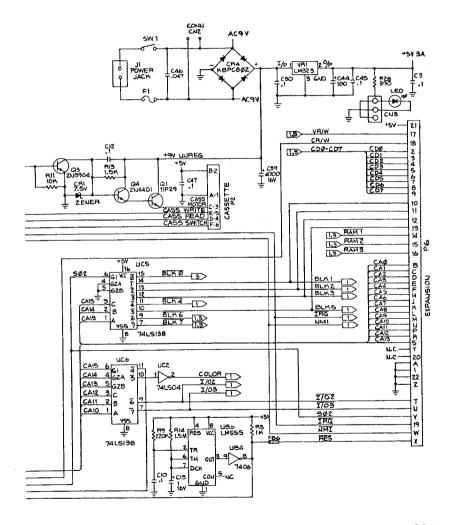

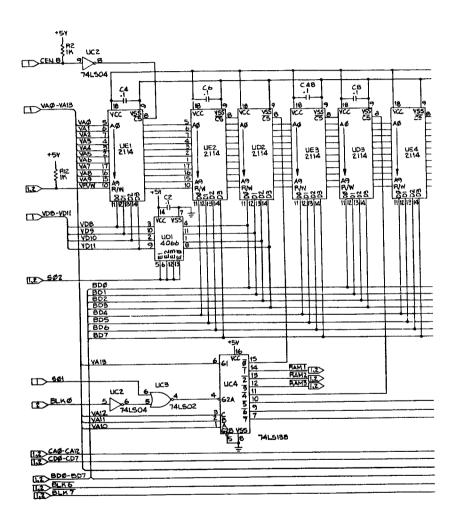

| i     | #5 — Circuit Diagrams | 257 |

|       | #6 — Monitor Inst.    | 263 |

- 2 6502 Microprocessor

- 3 Memory Usage and 6502 Instruction Cycle

- 7 Accumulator and Arithmetic

- 11 Addressing Modes

- 14 Processor Status Register and Use of Flags

- 16 Branches, Jumps and Program Counter

- 19 Stack Register and Its Use

- 21 Index Registers

- 23 Data Modify Instructions

- 24 Interrupts and Initialisation

- 27 Machine Code on the Vic

- 32 Writing Machine Code Programs

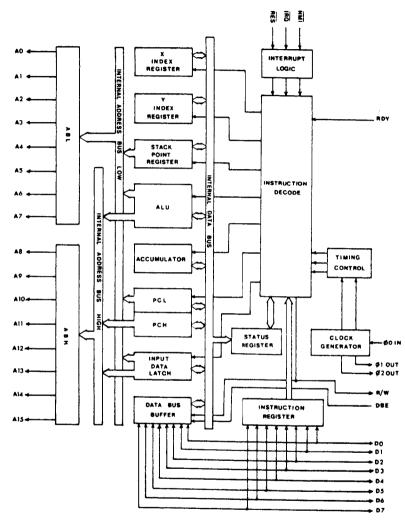

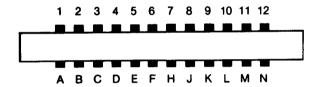

Fig. 1 — Block diagram of internal structure of 6502.

### THE 6502 MICROPROCESSOR

When a program is run on the VIC all the instructions are performed by one component, the microprocessor. There are a range of different microprocessors, this particular device is manufactured by MOS Technology and known as the 6502. It is an eight bit microprocessor, eight bits meaning that during each instruction or operation cycle, eight bits of data are operated upon or transferred simultaneously.

A block diagram of the internal structure (known as the system architecture) is shown in Figure 1. This may appear rather complex, but it can be divided into two sections. One called the control section. the other the register section. The control section lies on the right side of the drawing, the register section on the left. All the processing is carried out within the register section of the chip, instructions obtained from program memory are implemented by a series of data transfers within this section. Each of the 56 different instructions which the 6502 recognises involves a unique set of data transfers. It is the control section which recognises the instruction, and initiates the correct sequence of data transfers. The instructions enter the processor via the data bus and are latched into the instruction register to be decoded by the control logic. Since most instructions require more than one data transfer within the register section, a source of timing signals is required to ensure the correct sequence, this is done by the timing control unit.

Each data transfer which takes place within the register section, is the result of the decoding of the instruction register and the timing control unit by the control logic, whose outputs enable the relevant registers. When programming at a machine level a primary concern is the control and manipulation of data within the processors registers. To understand the function of the microprocessors instruction set, one must understand the function of its registers.

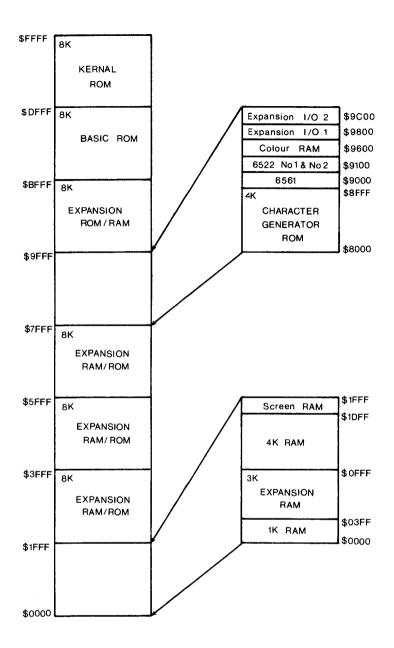

### MEMORY USAGE AND THE 6502 INSTRUCTION CYCLE

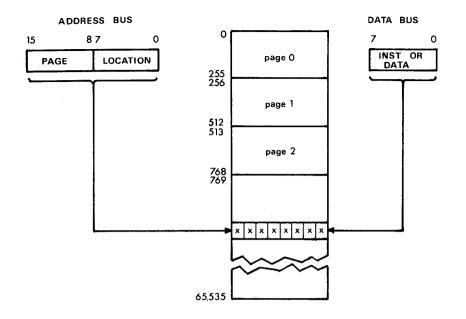

The 6502 microprocessor has a 16 line address bus, this enables it to access 2<sup>16</sup> or 64K of memory. Any one of the 65,536 memory locations can be accessed by the processor placing the correct binary value corresponding to the memory location on the address bus. The eight bits or byte of data located at the addressed memory location can then be read, or if required changed, via the eight line data bus. Since all the processor registers and memory are only eight bits long it requires two bytes to specify a sixteen bit memory address. The bottom eight bits are referred to as the high order address. By dividing the 16 bit address into two 8 bit sections the entire addressable memory area can be split into logical blocks, or pages. Memory within each page can be addressed using the low order address byte, each page has 256 memory locations and there are 256 pages. Page zero starts at location 0 and ends at address 255, page one goes from address 256 to 511. Apart from two important exceptions the concept of paging is not important to the programmer, these being, page one which contains the processor stack, and page zero which has special addressing modes.

It is usual to express memory addresses and their data contents in hexadecimal notation, this being easier to write than binary, yet more easily converted into binary than a decimal value. The convention is to identify hexadecimal values by preceding the value with a dollar sign, this prevents any confusion as to whether the value is in hexadecimal or decimal. In hexadecimal any address is represented as a four digit value, the first two digits being the high order address byte and the bottom two digits the low order address byte. The paging concept is thus clearly seen in a hexadecimal address. Any data value is represented in hexadecimal as a two digit value.

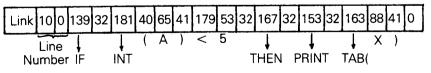

Memory is used by the processor for the storage of both programs and data, the data can be either included within the program, usually as constants, or in separate data tables. Programs can be stored either in RAM or ROM memory but variable data can only be stored in RAM memory. Each instruction in a machine code program requires between one and three bytes of memory. With a one byte instruction the data on which it operates is stored in one of the processor registers. A two byte instruction consists of the instruction first followed by a one byte operand, this can be either a zero page address or a data constant. An instruction occupying three bytes contains the

Fig. 2 — Relation between address, data, and memory location.

| Instruction       | Memory Contents | Function | Start Address |

|-------------------|-----------------|----------|---------------|

| 1 D 4 ((000       | \$A9            | INST     | + 1           |

| LDA#\$02          | \$02            | OP       | + 2           |

| STA \$0253        | \$8D            | INST     | + 3           |

|                   | \$53            | OP LSB   | + 4           |

|                   | \$02            | BP MSB   | + 5           |

| CLC               | CLC \$18        |          | + 6           |

| A D C ##50        | \$69            | INST     | + 7           |

| ADC#\$50          | \$50            | OP       | + 8           |

| STA <b>z</b> \$55 | \$85            | INST     | <b>+</b> 9    |

| 31M 2000          | \$55            | OP       | + 10          |

| RTS \$60          |                 | INST     | + 11          |

Fig. 3 — How a program is stored in memory.

instruction followed by a full sixteen bit address in the form; low order byte followed by high order byte.

When the processor executes the program instructions stored in memory it goes through a fixed instruction cycle, this gets the instruction from memory, performs the instruction, and then repeats by getting the next instruction, and so on until the end of the program. There are three stages in the instruction cycle, they are;

- 1) fetch the instruction.

- 2) decode the instruction.

- 3) execute the instruction.

Fundamental to the operation of the instruction cycle is the internal processor register called the program counter. The program counter holds the 16 bit address of the next instruction, and the first stage in the instruction cycle is to transfer the contents on the program counter onto the address bus. The instruction located at that memory address is then transferred to the processor instruction register. The second phase of the cycle is to decode the contents of the instruction register to generate the correct sequence of internal and external signals to perform the execution stage of the cycle. The execution phase of the cycle depends on the instruction and will include the fetching of any operand bytes plus the manipulation of one or more processor registers. After fetching an instruction or an operand byte the program counter is incremented by one so that at the end of the instruction cycle it contains the address of the next instruction and the process is repeated.

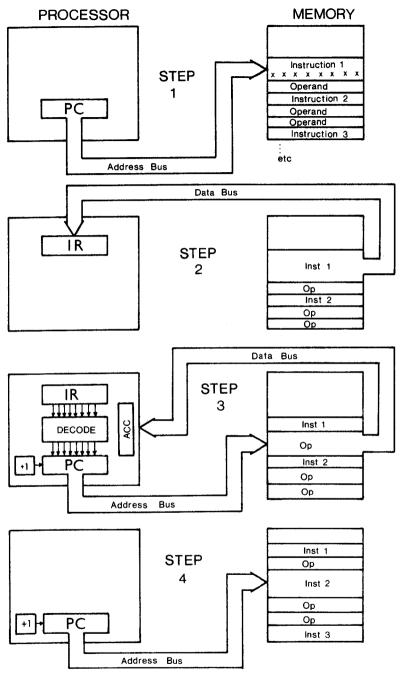

Fig. 4 — Sequence of processor operations in executing an instruction.

- Step 1 program counter points to location of instruction by placing the memory address on the address bus.

- Step 2 the instruction code is transferred from memory to the instruction register where it is decoded.

- Step 3 the program counter is incremented to point to the operand byte of the instruction in the following memory location, this byte is placed in the accumulator. The decoded instruction then results in a specific operation being performed on the byte in the accumulator.

- Step 4 The program counter is incremented to point to the next instruction in memory and the sequence returns to step 1.

Fig. 4

### THE ACCUMULATOR AND THE ARITHMETIC UNIT

The accumulator has no exact function, it is a general purpose register. To move a byte of data from one part of memory to another it must be temporarily stored in the accumulator. The accumulator is also used to store the intermediate and final results of a logic or arithmetical operation.

Data transfers between the accumulator and memory (since the VIC is a memory mapped system this also includes I/O) are very important and account for about 40% of all the instruction used in a machine code program. To move a byte of data from one memory location to another requires two instructions:

LDA,M1 — Load accumulator with contents of first memory location.

STA,M2 — Store contents of accumulator in second memory location.

Memory locations M1 and M2 are accessed by one of a variety of addressing modes, these will be looked at later in this section. Having loaded a byte of data into the accumulator the processor can be instructed to perform arithmetic or logical operations upon it. Only about three percent of all instructions in a program are arithmetic or logical operations.

Since the 6502 is an eight bit machine all the arithmetic and logical operations are between two eight bit numbers. The arithmetic or logical operation is performed in the ALU or arithmetic logic unit, this requires that one of the operands is in the accumulator and the other is in a memory location. The result of the operation is placed in the accumulator. Placing the results in an eight bit accumulator causes a problem when adding two numbers whose sum is greater than 255. . This is overcome by giving the accumulator a ninth bit, called the carry. The carry bit, or flag, is one bit in the processor status register, and is set when the contents of the accumulator exceed 255. This applies to the performance of binary arithmetic by the processor, the 6502 is fairly unique in that it can also do decimal arithmetic. In this mode each byte contains two binary coded decimal numbers. numbers from 0 to 99 can be stored as a single byte. As in the binary mode, the carry flag is set when the addition of two numbers gives a result greater than 99. The processor is placed in the decimal mode by a "set decimal mode" instruction, SED, which sets another bit within the processor status register.

There are two basic arithmetic instructions, ADC — which is "add memory to accumulator with carry", and SBC — which is "subtract memory from accumulator with borrow". Both instructions can be either binary or decimal in nature and can use a variety of addressing modes to indicate the memory location.

The ADC instruction adds the value of the data in the memory location, plus the carry from the previous operation, to the value in the accumulator, storing the results in the accumulator. If the result exceeds 255 in the binary mode, or 99 in the decimal mode, then the carry flag is set, if the result is zero then the zero flag is set. An example, if we want to add the two numbers, 25 and 189, and store the result in memory location 10 (decimal) we could use the following sequence of instructions:

CLC 18 (this clears the carry flag) LDA 25 A9 19 (Load accumulator with 25)

ADC 189 69 BD (Add 189 to accumulator and carry)

STA 10 8D 0A 00 (Store result in location 10)

The instructions in the left column are in mnemonic code, followed by a decimal number or memory location. The same sequence of instructions appears on the right as hexadecimal values. Addition of two numbers where one or both have values greater than 255 needs a process known as multiple precision addition, calling for the use of the carry flag. Adding two sixteen bit numbers, requires two additions. The carry is first cleared and the two lowest order bytes, (a sixteen bit number would be stored in two bytes of memory) added together. The result of this addition is stored in a memory location as the low order byte of the result. Now the two high order bytes are added, plus any carry generated by the first addition, the sum stored as the high order byte of the result. Using this method numbers of any size can be added together, whether the processor is in binary or decimal mode.

Addition can be performed on signed numbers. Positive numbers added to negative numbers, or two negative numbers added. The sign is stored as bit seven of the highest order byte, a zero for positive and a one for negative. Addition takes place as in ordinary arithmetic, the only exception being that the carry flag for the highest order byte is replaced by the overflow flag. This performs the same function but records an overflow or carry from bit seven, rather than bit eight. Negative numbers are stored not as ordinary binary numbers but as

two's complement, which is best described as the inverse of that number minus one. All the ones become zeros and vice versa for all bits, except bit one, thus binary five is normally 00000101 — in two's complement form it become 11111011.

The SBC instruction subtracts the value of data in a memory location (and borrow) from the value in the accumulator, storing the result in the accumulator. Two's complement arithmetic is used throughout. The borrow flag is the same as the carry flag used in addition, whereas before an addition the carry flag is always cleared, before a subtraction it is always set. The result of subtraction affects the carry or borrow flag, it is set if the result is greater than or equal to zero. Similarly for subtraction of signed numbers the overflow flag is set if the result exceeds +127 or —127 for single precision seven bit arithmetic. The SBC instruction can be used with either binary or decimal numbers with both multiple precision and signed arithmetic. To subtract two decimal numbers, say, 18 from 27 use the following sequence of instructions, the decimal mode is used to illustrate its function:

| SED    | F8       | (set decimal mode instruction)            |

|--------|----------|-------------------------------------------|

| SEC    | 38       | (set borrow flag)                         |

| LDA 27 | A9 27    | (load accumulator with 27)                |

| SBC 18 | E9 18    | (subtract 18 from accumulator and borrow) |

| STA 10 | 8D 0A 00 | (store result in location 10)             |

The instructions on the left are in mnemonic code, on the right in hexadecimal, note that in the decimal mode the hexadecimal and decimal numbers are the same.

The 6502 instruction set does not include instructions to perform multiplication or division. Users requiring these functions must write special subroutines to perform them, or use the subroutines within VIC Basic. Multiplication is a process of repeated addition:  $3 \times 5$  is the same as 5 + 5 + 5. For large numbers this could be a lengthy process, and programming tricks are required to minimise this. Division is a process of repeated subtractions: 15/5 can be performed as the following sequence, 15 - 5 = 10, 10 - 5 = 5, 5 - 5 = 0, since three subtractions were required, the answer is 3. As with multiplication, programming techniques are needed to reduce the time taken to divide large numbers.

Besides arithmetic operations the ALU can perform logical operations between data in memory, and the accumulator. There are

four such instructions AND, BIT, OR and EOR. The AND instruction performs a bit by bit logical AND operation between a memory location and the accumulator, storing the result in the accumulator. This operation can be used to reset or mask a single bit or group of bits in a memory location. In the decimal mode each byte holds two digits. the AND instruction can be used to extract one digit. Where there is a zero in the operand, there is a zero in the result. To mask out the most significant decimal digit stored in the bottom four bits. accumulator is ANDed with 00001111 or hexadecimal OF (load the accumulator with decimal 25) Δ9 25 I DA 25 (AND the accumulator with 00001111 binary) AND 0F (hex) 29 F0 8D 0A 00 (store the result in location 10) STA 10 On running this program location 10 will contain 05, the 2 being masked out and replaced by a 0. The BIT instruction is identical to the AND, except that the result is not stored in the accumulator and only the status register flags are set.

The OR instruction performs a binary OR on a bit by bit basis between the contents of the accumulator and a memory location, the result is stored in the accumulator. The main use of this instruction is to set a bit or group of bits in a memory location, a logical 1 in the operand field produces a 1 in the corresponding bit of the result. The EOR or "Exclusive OR instruction" is identical to the OR, except that a logical 1 appears in the result only if there is a 1 in the operand field, and a 0 in the accumulator for the corresponding bit. The main use of the EOR instruction is to produce the two complement of a byte.

### ADDRESSING MODES

Every instruction in a machine code program contains information on the position of the data on which that instruction will operate. The same instruction can exist in several forms depending on where the data is located and each of these forms is referred to as an addressing mode. There are thirteen different addressing modes and most instructions can be performed in more than one mode. The LDA instruction can use one of eight different modes of addressing. The thirteen address modes can be divided into seven basic modes and six modes which are combinations of one of the basic modes and the indexed addressing mode.

Implied

Accumulator

Immediate

Absolute

Zero page

Relative

Indirect

Absolute X indexed Absolute Y indexed Zero page X indexed Zero page Y indexed Indirect indexed Indexed indirect

The simplest mode is Implied addressing, which is used exclusively by single byte instructions operating on the internal processor registers. In an instruction like CLC (Clear Carry) no data is accessed therefore no address is required. It is implied that a register, in this case the Status Register, is to be operated upon.

Accumulator mode addressing is used in instructions which perform logical operations on data in the accumulator. This mode is a version of implied addressing and all instructions are single byte.

Immediate addressing is used whenever the programmer wants to perform an operation using a constant. To put a value of, say 25, in the accumulator we would use the LDA instruction in the Immediate mode. In this form of addressing the data is stored in the byte immediately following the OPCODE.

Neither the Immediate or Implied addressing modes use a memory address where data is stored, and are of little use in operations with variables. To address any location in memory would require a full sixteen bit or two byte address stored in the Operand part of the instruction. This address points to a memory location where the variable upon which the operation being performed is currently located, or is to be stored. This form of addressing is known as "Absolute addressing".

A shortened form of absolute addressing can be used when the memory location being accessed lies on page zero of memory. This is the only case where the concept of paging has any importance in the 6502, page zero is just the bottom 256 memory locations. This is called "Zero Page Addressing", and uses a single byte address to point to the location of data within page zero. A two byte Zero page address mode instruction is much faster than three byte Absolute addressing and it is good practice to store all variables in page zero. When running machine code programs on the VIC only the bottom 144 bytes of page zero should be used, storing data in locations above this will probably cause the machine to crash.

A special form of addressing is used exclusively by branch and jump instructions, known as "Relative addressing". In this addressing mode the instruction is followed by a single byte Operand. This does not specify an address as in zero page addressing, but a displacement from the address where the branch instruction is stored. Since the displacement must be either positive or negative, bit eight is used to signify the jump direction, this allows the jump to be up to 127 bytes forward or 128 bytes backward.

In some programs it may be necessary to have a computed address rather than a fixed address, as in absolute addressing. This is done using indirect addressing, instructions in this mode have just a single eight bit address field which points to the effective address as two bytes in page zero. The data address is thus not stored directly in the Operand field of the instruction, but, indirectly in page zero, all the indirect addresses are indexed except for the JMP instuction.

Indexed addressing uses the contents of one of the two index registers as an offset to the address stored as the Operand part of the instruction. The address stored in the Operand can be either an absolute two byte address, or a zero page single byte address. This gives a total of four different indexed addressing modes, two for each index register. The primary use of indexed addressing is in the access of successive memory locations used for the storage of a table or block of data.

### THE PROCESSOR STATUS REGISTER AND THE USE OF FLAGS

The processor status register occupies a very important position in the system architecture of the 6502. It is an eight bit programmable register, unlike the other registers and its function lies between the control and register section of the processor. It is the only register which actually affects the control logic. Seven of the eight bits are used, and each bit, or flag, has a specific function.

Flags fall into three categories, those controllable only by the programmer, those controllable by both programmer and processor, and lastly those controlled solely by the processor. Only one flag falls into the first catagory, the Decimal mode or D flag, occupying bit three of the status register. This flag controls whether the processor performs binary or decimal arithmetic. It can be set by a SED instruction, after which all arithmetic is performed in the decimal mode, until the D flag is cleared by a CLD or clear decimal mode instruction.

Three flags fall into the second category: Carry, Overflow and Interrupt disable. The Carry or C flag is located in bit 0 of the status register, it is modified either by the results of certain arithmetic operations or by the programmer. The carry is also used as a ninth bit during arithmetic operations or by the shift and rotate instructions. The instruction used to set the carry flag is SEC, it can be cleared by CLC.

The Overflow or V flag occupies bit six of the status register, and is used during signed binary arithmetic to indicate that the result was of greater value than could be contained within the seven bits of the signed byte. The V flag has the same meaning as the carry flag, but also indicates that a sign correction routine must be used if this bit is "on", since the overflow will have erased the sign in bit seven. The programmer can only clear the V flag by using the CLV instruction.

The Interrupt disable, I flag, controls the operation of the microprocessor interrupt request input, and is located in bit two of the status register. Interrupts play a very important part in the VIC's design, and each time there is an interrupt the I flag is set by the processor. This stops the processor being interrupted by more pulses on the IRQ line until the interrupt handling program has been completed with a return note an interrupt instruction clearing the I flag.

The I flag can also be set by the programmer with an SEI instruction to prevent the processor being interrupted, as during a precision timed loop subroutine. At the end of such a program the interrupt line can be returned to its normal function by clearing the I flag with a CLI instruction.

The last three flags: Zero, Negative and Break, are controlled solely by the processor. The Zero and Negative flags are either set or reset by nearly every processor operation. The Zero or Z flag is set by the processor whenever the result of an operation is 0, as when two numbers of the same value are subtracted from each other. The Negative or N flag is set equal by the processor to bit seven of the result of an operation. One of its primary uses is during signed binary arithmetic, if the N flag is set then the result is a negative number. The Break or B flag is set by the processor during an interrupt service sequence. The Z flag occupies bit one, the N flag bit seven and the B flag bit four of the status register.

The seven status bits or flags in the status register each have a meaning to the programmer at a particular point in the program. Although the carry and overflow flags are used in arithmetic operations the major use of flags is in combination with the conditional branch instructions. This gives the programmer the capability of incorporating decision making instructions within a program, to test a flag, and, depending on the state of that flag, take one or two courses of action. A conditional branch is functionally the same as the IF... THEN GOTO ... statement in Basic. There are a range of instructions performing different functions different flags. Anyone writing a machine code program must keep track of the expected state of all flags at every instant throughout the program. Failure to do this is one of the commonest causes of a program not working or producing the wrong result. An example would be failure to clear the carry flag before an addition. On odd occasions it would have been set by a previous instruction, and thus give rise to erroneous results.

# BRANCHES, JUMPS AND THE PROGRAM COUNTER

To understand the use of branch and jump instructions the concept of program sequencing must be understood, and its control by the program counter. The program counter, or PC, consists of two eight bit registers. Like the other registers they communicate with the internal processor data bus, but the outputs are also connected to the sixteen lines of the address bus. One of the PC registers is connected to the bottom eight address lines and is called PCL, the other, the PCH is connected to the eight high order address lines. Although two eight bit registers, they function like a single sixteen bit register. It is the program counter which controls the addressing of memory, by being a program, or data address pointer and, as such it contains the address of the next memory location to be accessed.

At the beginning of the program the PC must contain the address of the first instruction. This is one of the functions of the operating system reset software. It is also preformed by the SYS and USR commands when entering a machine code program from Basic. The instruction fetched from memory is stored in the instruction register. to be decoded by the control logic. This process takes one clock cycle. during which time the program counter is incremented by one to point to the next memory location. The processor usually requires more than one byte to interpret an instruction, this first byte contains the basic operation and is known as the OP CODE. The following one or two bytes, known as the OPERAND, contain either a byte of data or the address of the data on which the operation will occur. An instruction may require up to three sequential memory locations, the program counter first points to the OP CODE which is fetched from memory and stored in the instruction register. The PC is incremented and points to the next memory location, the contents of which are fetched and stored in the ALU, in a three byte instruction this will be the low order address of the data. The program counter is again incremented and the high order address fetched from the third memory location. The processor then latches the two bytes of the address onto the address bus via the ALU, fetches the data, and performs the operation. Having completed the operation, which usually takes about four clock cycles, the processor increments the program counter to point to the next instruction and the process is repeated. In this manner the program counter will continue to advance until it reaches the maximum memory location, fetching instructions and addresses.

A sequential program would lack a feature fundamental to computing, the ability to test the result of an operation, and implement various options based on the results of the test. Firstly flags can be used to test the result of an operation, secondly the contents of the program counter must be changed to point to the start of a new program. The simplest way of changing the contents of the program counter is with the JMP or "Jump to new location" instruction. This as its name implies does not perform any tests on the results of a previous operation. It simply loads a new sixteen bit address into the program counter thereby forcing the processor to start operating at the new address. The JSR or "Jump to Subroutine" instruction is similar to JMP except that the current contents of the program counter are saved on the stack to be restored on the completion of the subroutine by an RTS, "Return from Subroutine" instruction.

There are eight different conditional branch instructions, they can be divided into four groups, each testing the state of one of the status register flags. The four flags tested by the conditional branch instructions are: Carry, Zero, Negative and Overflow, one instruction tests if the flag is set, and the other if it is clear. The two instructions for the Carry flag are BCC or "Branch on Carry Clear" and BCS or "Branch on Carry Set". The Operand contains the address to which the program jumps if the condition being tested is true. The addressing mode used is unique to conditional branch instructions, it is called relative addressing.

In relative addressing the new address is stored as just one byte, which is added to the current contents of the program counter. To enable the program to branch both forwards and backwards the relative address can be either a positive or a negative number. The fact that relative branch addresses are stored as a signed single byte limits the maximum size of the branch to either 127 bytes forwards or 128 bytes backwards, this may seem a limitation but in practice it is

The eight conditional branch instructions are: BMI — Branch on Result Minus Testing the N flag BPL — Branch on Result Plus BCC ---Branch on Carry Clear Testing the C flag BCS — Branch on Carry Set

BEQ - Branch on Result Zero

Testing the Z flag

BNE — Branch on Result Not Zero

BVS — Branch on Overflow Set

Testing the V flag

BVC — Branch on Overflow Clear

Most operations involve the setting of one or more flags, but a small group of test instructions are specifically designed to set flags for testing by a branch instruction. The most commonly used is the "Compare Memory and Accumulator" or CMP instruction. It allows the programmer to compare a value in memory to one in the accumulator without altering the value in the accumulator. If the two values are equal the Z flag is set, otherwise it is reset. The N flag is set equal to bit 7 and the carry flag is set when the value in memory is less than or equal to that in the accumulator. The BIT instruction tests single bits in memory with the corresponding bits in the accumulator.

### THE STACK REGISTER AND ITS USE

The stack register is mainly concerned with the handling of interrupts and subroutines. It is an eight bit register, its function is identical to that of the program counter since it is an address generator. It is used to point to an address in page 1 of memory, (locations 256 to 511), known as the "Stack". The stack is a set of memory locations starting at 511 and filled downwards from that location with a maximum size of 256 bytes. It is organised as a LIFO or "Last In First Out" structure, which means that the last byte of data stored on the stack is the first byte to be accessed. Every time data is pushed onto the stack the stack pointer is decremented by one, and each time data is pulled off the stack, the stack pointer is incremented by one. The addressing of the stack is independent of the program and based purely upon chronological events. The stack is used as a temporary data store, the most common data being re-entrant addresses generated by subroutines and interrupts.

Every time a subroutine is called in a machine code program the current contents of the program counter are saved. On returning from the subroutine the program can be re-entered at the correct location. Similarly every time the processor is interrupted the current address in the program counter is saved before the processor performs the interrupt servicing routine. A subroutine may call other subroutines, requiring the storage of several re-entrant addresses in the stack. The last re-entrant address stored is the first address reloaded into the program counter at the end of the subroutine, hence the LIFO structure of the stack. The calling of subroutines by other subroutines is termed "subroutine nesting" and is a common occurrence in machine code programs. The size of the stack in the 6502 limits the user to 127 levels of nesting, usually far more than is needed. Basic subroutines also use the stack for the storage of the return address pointers and register contents.

A subroutine is called by a JSR or "Jump to Subroutine" instruction. This pushes the current contents of the program counter onto the stack. A location stored as the Operand field is then loaded into the program counter. This causes the processor to jump to a new section of the program and start execution from the location in the program counter.

The return from a subroutine to the main program is accomplished by he RTS or "Return from Subroutine" instruction. This loads the

return address from the stack into the program counter. It also increments the program counter to point to the instruction following the JSR. The stack pointer is also incremented to point to the next subroutine address if any.

The stack can be used by the programmer as a temporary storage location for data passed to a subroutine. The programmer needs a set of instructions to allow him to put data onto the stack and read it back. The current contents of the accumulator can be transferred to the next location on the stack by the PHA or "Push Accumulator onto Stack" instruction. Data can be read from the current location pointed to by the stack pointer into the accumulator, by the PLA or "Pull Both instructions instruction. Stack" Accumulator from cause the stack pointer to be incremented or automatically decremented by one. An example of data storage in the stack is saving the contents of the processor status and index registers when a subroutine is called. The contents of the status register can be pushed onto the stack by the PHP "Push Processor Status on Stack" instruction and then transferred from the stack back to the status register by the PLP "Pull Processor Status from Stack" instruction. To save the contents of the index registers they are first transfered to the accumulator and then placed on the stack. When writing any machine code routine for the VIC which will be called from a Basic program it is very important to first save the contents of the processor accumulator and index registers on the stack. The contents of these registers are then restored prior to returning to Basic. Failure to do this will result occasionally in system crashes.

Normally the stack pointer points to a location in page one, the location being automatically incremented or decremented by the processor as required, but in some situations the programmer has to be able to change the stack pointers contents. The stack pointer is loaded by transferring the contents of the X index register to the stack pointer with a TXS "Transfer Index X to Stack Pointer" instruction. This instruction is used at the beginning of a program to initialise the stack pointer, it is performed automatically on the VIC as part of the power up reset routine. Re-initialising the stack on the VIC causes problems, usually resulting in a crash and should thus be avoided. The current contents of the stack pointer can be read by loading it into the X index register with a TSX "Transfer Stack Pointer to Index X" instruction.

### THE INDEX REGISTERS

Having a fixed address in the Operand field of an instruction poses problems when accessing a sequential block of data, such as a table or an input buffer. One method would be to use a string of load instructions in the form, load data from address 1 - perform operation — load data from address 2 — perform operation and so on. This is obviously highly wasteful of memory space, it would be more efficient if this program was written as a loop. To do so would require that the address stored as the Operand field of the load instruction is incremented each time the program goes round the loop. In this way the Operand address will always be pointing to the next byte of data to be accessed. This method is useful, but, execution time is programming greater than in the straight line considerably technique, also it is often undesirable to use a self modifying program.

A more sophisticated approach is the use of a counter, the contents of which are automatically added to the address in the Operand field of the instruction. Such a counter is called an Index register. There are two Index registers in the 6502, both are eight bit registers, labelled X and Y. They are used by instructions in one of the indexed addressing modes. The simplest is absolute indexed addressing, in this mode the contents of one Index register is added to the address in the Operand field of the instruction, giving a new address from which data is to be accessed. The fact that the Index registers are only eight bit registers limits the maximum size of data block accessed using indexed addressing to 256 bytes. In practice the majority of tables are shorter, it is not therefore a significant limitation. If longer tables are required then programming techniques, such as indirect indexed addressing, are used to overcome this limitation.

The Index registers are controlled and manipulated by a range of special instructions. A number can be loaded to, or stored from the Index register and a memory location, by the LDX, LDY and STX, STY instructions. Similarly the contents of the Index registers can be compared with a value in memory to test if a conditional branch should take place by using the CPX and CPY instructions. The contents of an Index register is changed to point to the next address by increments or decrementing it by one. To count up, the instruction used is INX or INY, to count down DEX or DEY. The remaining Index register instructions allow the transfer of the contents of the accumulator into one of the Index registers and vice versa. TAX and

TAY transfer the accumulator contents into X and Y registers respectively and TXA, TYA transfer the Index register contents to the accumulator.

In some programs it may be necessary to have a computed address, rather than a base address with an offset, as in absolute indexed addressing. This is done using indirect addressing, instructions in this mode have just a single eight bit address field which points to the effective address as two bytes in page zero. The data address is thus not stored directly in the Operand field of the instruction but, indirectly in page zero, all the indirect addresses are indexed except for the JMP instruction. Two modes of indirect addressing are possible, Indexed Indirect and Indirect Indexed Addressing.

Indexed Indirect addressing index register X is added to the Operand zero page address. This points to locations where the sixteen bit data address is stored. One of the major uses of this addressing mode is in retrieving data from a table or list of addresses, as in polling 1/0 devices or performing string operations.

Indirect Indexed addressing the sixteen bit address pointer in page zero is first accessed then offset by the contents of index register Y to give the true data address. The location of the pointer is fixed, whereas in the indexed indirect mode it is variable being offset by the contents of index register X. Indirect indexed addressing combines the advantage of an address that can point anywhere in memory with the offset capability of the index register. It is a particularly powerful method of accessing the nth element of a table, providing the start address is stored in page zero.

# **DATA MODIFY INSTRUCTIONS**

A small group of instructions are not associated with any particular processor register. They are classified as read/modify/write instructions. They all read data from a memory location or accumulator, modify it in a particular way and store the modified data back into memory or the accumulator. These instructions perform four different data modifications, shift, rotate, increment and decrement.

A shift instruction is one which takes the contents of the accumulator or a memory location and shifts all bits one bit to the left or right. An example is the LSR-Logical Right instruction, here the data in the accumulator or memory is moved one bit to the right, bit 0 is placed in the carry flag and bit seven set to zero. Similarly the ASL-Arithmetic Shift Left instruction moves the data one bit to the left, bit seven is stored in the carry flag and bit 0 set to zero. Repeated shifts in the same direction will eventually result in the entire byte being set to zero. Herein lies the difference between a shift and a rotate instruction. In a rotate instruction the contents of the carry flag is stored in the bit emptied by the shift, thus no data is lost in a rotate instruction. The ROL-Rotate Left instruction shifts the contents of the accumulator or addressed memory left 1 bit with the carry stored in bit 0 and bit 7 stored in the carry flag. With ROR-Rotate Right instruction the data is shifted right 1 bit with bit 0 shifted into the carry and the carry shifted into bit 7. The shift and rotate instructions have a unique form of addressing, in addition to the normal forms, and is known as accumulator mode addressing. It indicates that the instruction is to operate on the accumulator rather than on a memory location.

Besides shift and rotate the contents of a memory location can be incremented or decremented. INC-Increment Memory by One adds one to the contents of the addressed memory location. DEC-Decrement Memory by One subtracts one in two's compliment form from the contents of the addressed memory location. The main use of increment and decrement is with counters such as table pointers.

# INTERRUPTS AND INITIALISATION

The processing of interrupts is important for the operation of the VIC system. As seen in Section 4 all peripheral 1/0 is interrupt driven, a knowledge of interrupts is thus required by anyone using the user port or the other 1/0. There are three input lines which can cause the processor to halt on completion of the current instruction. On receipt of one of these inputs the program counter is stored on the stack and the processor causes the program to jump to an interrupt servicing routine at an address pointed to by the contents of one of the interrupt vectors. These three lines are Reset, Interrupt Request or IRQ, and Non-Maskable Interrupt or NMI. All three lines can be used by external devices attached to the VIC memory expansion port. Their function can be controlled by the programmer thanks to the RAM vectored address table which allows user written routines to replace the system routines governing interrupts and reset.

The only way a programmer can change the sequence of operations is to load a new address into the program counter. If this were true then an external event could not effect the program sequence, unless the program was written to periodically check for an input. Most inputs are asynchronous, meaning that for an input to occur at the same time as the program is checking for inputs is extremely unlikely. If an input pulse occurred just after an input check, then not until the next check would that pulse be input to the computer. During the interval between checks; data at the input may have changed resulting in the loss of information. To overcome such a data loss the processor could be programmed to wait for the data, but this would mean the processor spending most of its time doing nothing.

The problem of having the processor wait for an input is overcome by having a special line signal the processor whenever an input occurs, an interrupt. This considerably simplifies programming, making it unnecessary to repeatedly use an input testing subroutine or have the computer wait for an input. The two interrupt lines used to signal to the processor that an input is present are the IRQ line and the NMI line. By pulling an interrupt line low for at least 20 microseconds an input device can signal that it wishes to send data to the processor. This forces the processor to finish its current instruction, store the program counter and status register on the stack and jump to a memory location pointed to by the interrupt vector. There are two interrupt vectors that for the IRQ line are located at 65.534 and 65.535.

for the NMI line at 65,530 and 65.531. The reset vector is located at 65,532 and 65,533.

The processor could be interrupted before it was able to retrieve data from an interrupt initiated input. To prevent this the programmer can disable the IRQ line and prevent further interrupts by setting the I flag in the processor status register. This is done by the first instruction in the interrupt handling subroutine. SEI-Set Interrupt Disable, A CLI — Clear Interrupt Disable instruction clears the I flag and allows the processor to be interrupted as normal. Having obtained data from the input the interrupt software can process it for use by the main program or respond with an output from an 1/0 port. Control is returned to the main program by the RTI-Return from Interrupt instruction. This pulls the contents of the processor status register and program counter off the stack restoring the processor to its pre-interrupt state. The NMI line can not be disabled with commands to the processor and will therefore always generate an interrupt irrespective of the state of the IRQ line and the Status register I flag. An interrupt on the NMI line therefore has a higher priority than an input on the IRQ line. The Reset line takes priority over both the interrupts causing all the system pointers to be reset and a Basic warm start initiated. If the Reset RAM vector address is changed then the user written reset routine which it points to must clear the processor registers, and reset the stack pointer to the beginning of the stack, before jumping to the entry point of the main program.

The VIC has two sources of interrupt, one from each of the peripheral 1/0 chips and either one can interrupt the processor. The interrupt line from one 1/0 chip (VIA No.2) is connected to the IRQ line (a timer on this chip generates regular interrupts which control update of the clock variable TI and keyboard scanning). The interrupt from the other 1/0 chip (VIA No.1) is connected to the NMI line and is used to generate a system restart when the Restore key is pressed. Each 1/0 chip has two interrupt inputs and one output connected to the IRQ or NMI lines. The function of these 1/0 inputs is dealt with in the sections on the 6522 VIA chip and the system 1/0.

An interrupt sequence can be created by the programmer without an input being present in the IRQ line, by use of the BRK — Break command. This instruction performs a software interrupt and causes program control to be transferred to the address stored in the interrupt vector. The main use of this instruction is in debugging a program, however, it calls one of the interrupt routines. Its use on the

VIC is not recommended. For VIC users a similar function is provided in the machine code monitor with none of the attendant problems of the BRK instruction.

## MACHINE CODE ON THE VIC

The VIC has an advantage over many other small micro computer systems in that it can be programed in both Basic and machine code. this gives the programmer the powerful option of using machine code subroutines in a Basic program. The VIC normally runs in the Basic mode and there are six ways of accessing the machine code environment. The first two use commands in Basic, these are, USR and SYS. Both commands access a machine code subroutine whose address is specified in the command or in a specific page zero location. The next four methods involve adding machine code subroutines into the operating system.

- 1 the Basic command USR(X) transfers program control to an address stored in locations 1 and 2, this address is user definable and will be the start of a machine code subroutine. The value X specified in the command is a parameter for use by the subroutine, this is evaluated and placed in floating accumulator No.1 starting at location \$0061. A parameter may be returned by placing it in the floating accumulator and providing it is in the correct format then this value will be assigned to the parameter variable.

- 2 the Basic command SYS(X) causes program control to jump to a machine code subroutine starting at address location X, where X is either a variable or a constant value equal to the decimal start address. Parameters can be passed between the Basic program and the machine code routine using POKE and PEEK commands to place or read values from specified memory locations.

- 3 if the machine code routines are located in ROM memory and start at memory address No.A000 then the VIC allows system control to jump to this location rather than the normal Basic interpreter when the machine is switched on. This is very useful since it allows the user to change the VIC system. This can be either adding extra commands to Basic, changing the I/O operation using the ROM and RAM jump vectors or simply bypassing the Basic and operating system software and replacing it with special custom software (this is commonly done for cartridge games).

- 4 add a program into the interrupt servicing routines, these are called sixty times a second by the keyboard scan interrupt signal. This method for example allows the scanning of 1/0 ports for an input, or selectively disabling certain keys on the keyboard. Any situation

where a program must be run concurrently with the main program could use this method.

- 5 involves inserting extra code into the CHARGOT subroutine which gets each line of Basic from memory prior to its execution by the interpreter. By intercepting each line of Basic before it is executed new Basic instructions can be added. The instruction being performed by a user written machine code subroutine. Both the method of inserting code into the interrupt routine and the addition of extra code into the CHARGOT subroutine will be dealt later with in full.

- 6 the RAM vector address table can be used to insert code into, or replace, any one of the Basic or system routines accessible through this table. This is similar to method 4 and could be used to reassign the functions of the interrupt lines or change the peripheral 1/0 handling routines.

The main reason for using machine code subroutines is that Basic is too slow for many purposes, especially when using the I/O ports or in special purpose display functions. A machine code routine is more than 100 times faster than the same program written in Basic. Another reason for using machine code is that one may want to change the operating system or use some of the operating system subroutines.

A machine code program which is loaded into RAM memory is best located at the top of memory. This area is used by Basic to store character strings, and to avoid these overwriting the machine code program the top of memory pointers must be changed. The top of memory pointers are set during power up diagnostics to the highest usable RAM location. The location of the top of memory and therefore the values stored in the top of memory pointer bytes depends on whether the VIC is fitted with any extension RAM. By lowering the value of these pointers a block of memory can be reserved exclusively for use by a machine code program. The operating system will regard the new top of memory pointers as containing the highest memory location usable by Basic. The pointer is stored as the low order byte in 51 and the high order byte in 52. As an example the following commands will lower the top of memory to location 4096:

POKE 51,0 : POKE 52,16 POKE 55,0 : POKE 56,16

CLR

Locations 55 and 56 are the top of strings pointers and must be set equal to the top of memory pointers at the start of the program, the CLR command resets all the variable pointers thereby clearing all variables used previously in the program. Care should be taken when locating machine code programs in RAM memory space that the memory area used is not also allocated to either video memory or character generator memory.

Of the two Basic commands used to call a machine code subroutine, SYS and USR, by far the most powerful and flexible is SYS. With the SYS command one simply specifies the subroutine starting location, thus if it starts at location 5000 it can be called with SYS 5000. Variables can be transferred between a Basic program and a machine code program by using PEEK and POKE. These read or write single or multiple byte values into memory locations allocated for the purpose and accessed by both programs. Transferring variables in this manner is easier than using the single floating point variable provided for the USR function. It also allows the transfer of more than one variable which USR does not. The only requirement with a SYS subroutine is that the last instruction in the subroutine is a RTS — return from subroutine, this automatically returns control to the Basic program.

The easiest way of entering a machine code program is to incorporate it into the Basic program using a simple loader, on running the program the loader POKES the values byte by byte into the correct locations. Another way is to use the machine code monitor which is part of the Programmers Aid ROM pack, a summary of all the commands in the monitor are given in Appendix 6. The monitor allows machine code program to be directly written into memory using hexadecimal code. It also allows programs to be saved and loaded onto tape in machine code format. To make the writing of machine code programs easier and avoid the necessity of hand encoding, a simple assembler and disassembler are included in the monitor. The monitor saves a machine code program by saving the block of memory where the program is located, far quicker than a corresponding Basic loader.

The only drawback with using the monitor to save and load a machine code program is that it will require a two part load, the first to load the machine code and the second to load the Basic program calling the machine code routine. The Basic program could be saved by the monitor together with the machine code, by saving the entire contents of user memory from location No. \$0400 up. Generally it is

```

20 RFM *BASIC LOADER FOR MACHINE CODE

30 REM *ROUTINE (EXAMPLE CODE ONLY)

40 尺巨門 米米米米米米米米米米米米米米米米米米米米米米米米米米米米米米米米

100 DATA 2048: REM **CODE START LOCATION

105 RFM **MACHINE CODE IN HEXADECIMAL

110 DATA 48,98,48,8A,48

120 DATA A9.13.20.D8.E3.A5.54.F0.09

130 DATA A9.11.20.D8.E3.C6.54.D0.F7

140 DATA A5,55,F0,09,A9,1D,20,D8

150 DATA 68,AA,68,A8,68,60

9000 DATA*: REM **END OF CODE

9005 REM **THE FOLLOWING LINES ARE THE BASIC

9006 REM **LOADER PROGRAM.

9010 READL

9020 READA$

9030 C=LEN(A$)

9040 IFA$="*"THEN9140

9050 IFC<10RC>2THEN9130

9060 A=ASC(A$)-48

9070 B=ASC(RIGHT$(A$,1))-48

9080 N=B+7*(B>9)-(C=2)*(16*(A+7*(A>9)))

9090 IFN<00RN>255THEN9130

9100 POKEL,N

9110 L=L+1

9120 GOTO9020

9130 PRINT"BYTE"L"=["A$"] ????"

9140 END

```

REATY.

best to use a Basic loader for short machine code programs which are called by the main Basic program. Longer machine code subroutines and machine code programs which stand alone and are not called from Basic are best saved using the monitor.

Another method of storing machine code programs is to store them within a Basic program as REM statements. To do this the machine code program must first be split into blocks, each block being less than 80 bytes long. Each byte of the machine code routines is stored as a character in the REM statements. The REM statements are stored as the first few lines of the Basic program. Each statement is first filled with dummy characters, the number of characters in each statement depends on the length of the block of machine code to be stored in that statement. The machine code monitor is then used to find each REM statement as it is stored in memory and replace the dummy characters with the code value for each byte in the machine code block. When the program is listed the REM statements will appear as a seemingly random collection of ASCII characters, each character however represents a byte of the machine code routine. When writing a machine code program to be stored in this way care should be taken to ensure that no absolute jump addresses are used within a block. this ensures that the routine is relocatable. Care should be taken to ensure that jump addresses from the main calling routine are suitably modified to allow for the six byte gaps in the program required for storage of line number, link address, command token and terminating 0, and the location of each routine.

# WRITING MACHINE CODE PROGRAMS

The prospect of writing a machine code program even a small one may seem fairly daunting, but providing one uses an orderly and disciplined approach to the problem it need not be difficult. A machine code program differs from Basic in the approach taken to its writing. Whereas a rough Basic program can be written and then polished up by inserting and changing lines, a machine code program must be written as the final version, any changes often necessitate rewriting and assembling the whole program. Machine code unlike Basic code is dependent on the exact position of instructions in memory. Adding a couple of instructions into the middle of a program means changing most jump, branch and data addresses. Machine code programs also require far greater attention to details like current flag status. programs must be very carefully planned before they are written. Unless this is done, writing a machine code program will require far greater effort than is necessary and the product far more prone to error. It is strongly recommended that before writing any programs in machine code yourself, you study some 6502 machine code routines, try to determine why the code was written in a particular way and what it does.

Stage one in planning a program is to define what the program is required to do, then break the problem into a series of steps. To demonstrate this consider the following example, to display all the ASCII characters on the screen.

Set the screen location pointer LOC to start of screen, address 32768 — set the ASCII character value CHAR to zero — store character code CHAR on screen at location LOC — increment LOC — increment CHAR — if CHAR is greater than 255 then all characters have been displayed and program ends, if not then go back and display next CHAR

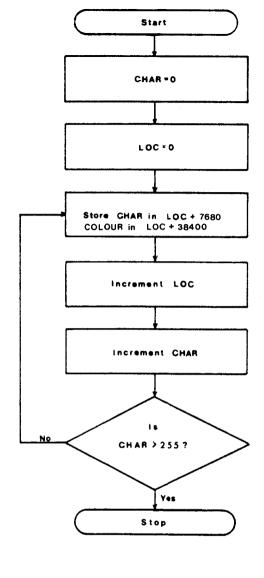

From this description we have defined that two variables CHAR and LOC are required, also the program structure requires a loop with a conditional test. For a short program like this a written description is not really required since one can easily remember what one wants the program to do. For longer programs it is an essential part of the process. From the written description one can construct a flow diagram such as the example in Figure 5. The flow diagram can be regarded as a pictorial version of the written description and as a result simpler to follow.

Initial Version

Fig. 5 — Preliminary flow diagram for example routine.

For long programs the flow diagram and written description can get very involved and confusing. It is good practice to split such a program into a series of self contained blocks or subroutine modules. Each module is then treated as a complete program, making program writing and debugging easier. The flow diagram shows the logical pathways through a program and most logical errors can usually be detected at this stage, saving a considerable amount of programming time.

Having drawn a flow diagram the next stage is the construction of a table of variables and locations of system subroutines called. In the example no system subroutines are used but two variables are required:

LOC — pointer to location in screen memory where character is to be stored.

CHAR — Value for ASCIII character to be displayed on screen.

It is important that the table contains all variables required, since when writing the program exactly the right amount of space in memory must be left to contain them.

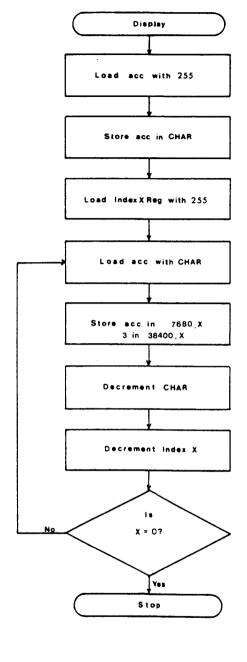

Having defined the logical flow of the program, the variables used and any system subroutines called, a start can be made on writing the program code. Probably the best way is first to draw an expanded version of the flow diagram. Breaking down each logical step into a series of substeps corresponding to a machine code instruction. In Figure 6 notice that the variable LOC is now stored as the contents of the X index register. Indexed addressing being the easiest way of putting data into successive memory locations. Also the index register (i.e. LOC) is loaded with 255 and decremented, rather than 0 and incremented as in the original flow diagram, since it is easier to test for zero than for 255. It should be noted that the coding of this example is not the optimum for either speed or compactness but rather for clarity so that the purpose of each command is clearly visible.

Having laid out the program in flow diagram form the next step is to write the actual code which will be used by the machine. There are three ways in which this can be done, the choice of which method is used depends on equipment available and the size of the program. The first method is to write the code by hand using a coding form using the instruction mnemonic or operand address/value in the opcode column, see Figure 7. Code written and assembled by hand can best be entered into the VIC memory by a Basic loader program.

Fig. 6 — Expanded flow diagram for example routine.

The second method again involves writing the code in mnemonic and label form by hand on a coding form, the assembler which is part of the monitor on the VIC Programming Cartridge is used to assemble the code and directly enter it into the VIC memory. The third method is best used for very long machine code programs and involves using a PET computer system (a 32K minimum with disks and printer) on which to write and develop the code. The code is written using the editor program in the assembler package, this creates a source code file on disk, the assembler uses this file during assembly to create an opcode file on disk which can be loaded into memory using the loader routine.

For hand assembly and coding of a program it is advisable to use a coding form such as that shown in the example, it helps to considerably reduce the number of errors occuring at this stage. On the first page of the coding form should be written a list of all variables, 1/0 locations and system subroutine entry points used. Each variable being assigned the number of bytes of memory which it will require. Most will be single byte but some will be two or three byte precision and in the case of character variables or data buffers memory required could be large. When storing a multiple byte numerical variable it is good practice to store the bytes in fixed order, with the least significant byte in the first location and the most significant byte in the last location. It is easier this way to keep track of which part of a variable is being dealt with. Also index registers can be used to access successive bytes of a variable in the same order that they are processed.

Program variables can be stored in any part of RAM memory not occupied by either programs or system variables. For maximum speed and reduced program size variables should be stored in page zero of memory, the bottom 255 bytes. On the VIC page zero is currently occupied by system variables. This area can be utilised if the memory locations used are carefully chosen. If Basic is not used, then the entire section of page zero used by the Basic interpreter for variable storage (locations 0 to 143) is available to the programmer. The remaining part of page zero is used by the operating system and may or may not be required by the machine code program. If both Basic and machine code are to be used together in the same program then the number of page zero locations available is limited (locations

|        | PROGRA                                   | .mD    | ISPLAY   |               | _                                                |            |   |   |                            |        |    |   |          |                                |  |  |

|--------|------------------------------------------|--------|----------|---------------|--------------------------------------------------|------------|---|---|----------------------------|--------|----|---|----------|--------------------------------|--|--|

|        | DATE _                                   | 20/6/7 | 9        |               |                                                  |            |   |   |                            |        |    |   |          | PAGE                           |  |  |

|        | ADDRESS<br>MSB LSB OPCODE LABEL MNEMONIC |        |          |               |                                                  | AD OPERAND |   |   | FLAGS<br>Z N C I D V CYCLI |        |    |   |          | COMMENT                        |  |  |

| 03     | 40                                       | _      | CHAR     | _             |                                                  |            | Ť | T | Ť                          | T      | Ť  | Ť |          | VARIABLE FOR ASCII CHARACTER   |  |  |

|        | ,                                        | A9     | DISPLAY  | LDA           | #                                                | 255        | T |   | Γ                          | Г      | T  | T | 1        | START - SET UP LOOP COUNT      |  |  |

|        | 2                                        |        | -        |               |                                                  |            | T | Г | Τ                          | T      |    | T |          | AND CHARACTER VALUE            |  |  |

|        | 3                                        |        |          | STA           | A69                                              | CHAR       | T | Т | Г                          | Г      | T  | Τ |          | INITIALISE 'CHAR'              |  |  |

|        | 4                                        | 40     |          |               | <del>                                     </del> |            | T | Τ |                            | T      | T  | T | 1        |                                |  |  |

|        | 5                                        | 03     |          |               |                                                  |            | T | T | T                          | r      | T  | t | ✝        |                                |  |  |

|        |                                          | A2     |          | LDX           | #                                                | 255        | t | T | Ħ                          |        | T  | r | <u> </u> | SET INDEX REG = 255            |  |  |

|        |                                          | FF     |          |               |                                                  |            | Т |   |                            | Г      | Г  | Γ |          |                                |  |  |

|        |                                          | AD     | NEXTCHAR | L'DA          | A66                                              | CHAR       | T |   |                            |        | Г  | T |          | GET 'CHAR'                     |  |  |

| -      | 9                                        | 40     |          | /             |                                                  |            | Τ |   | Г                          | Γ      |    | Γ |          |                                |  |  |

|        | A                                        | 03     |          |               |                                                  |            |   | Γ |                            |        | Γ  | Г |          | -                              |  |  |

|        |                                          | 9D     |          | STA           | A65,X                                            | \$1E00, X  | T | Г | П                          | Г      |    | Г |          | STORE AT START OF VIDEO RAM    |  |  |

|        | С                                        | 00     |          |               |                                                  |            | Г |   |                            |        | Г  | _ |          | + INDEX                        |  |  |

|        | D                                        | 1 E    |          | _             |                                                  |            |   |   | П                          |        |    |   |          |                                |  |  |

|        | £                                        | A 9    |          | LDA           | #                                                | 03         | Г | Г | П                          |        | Г  | Г |          | SET COLOUR = RED               |  |  |

|        | F                                        | 03     |          | /             |                                                  |            | Г |   | П                          |        | П  | Г |          |                                |  |  |

|        | 50                                       | 9D     |          | STA           | ABS,X                                            | \$9600, X  | Γ |   | П                          |        | Г  |   |          | STORE COLOUR IN COLOUR RAM     |  |  |

|        | 1                                        | 00     |          |               |                                                  |            | Π |   |                            |        | Γ. |   |          | AT \$9600, X                   |  |  |

|        | 2                                        | 96     |          |               |                                                  |            | П |   | П                          |        |    |   |          |                                |  |  |

|        | 3                                        | CE     |          | DEC           | Ads                                              | CHAR       |   |   |                            |        |    |   |          | PUT NEXT ASCII CHARACTER       |  |  |

|        | 4                                        | 40     |          |               |                                                  |            |   | П | П                          |        |    |   |          | IN 'CHAR'                      |  |  |

|        | 5                                        | 03     |          |               |                                                  |            | П | П | П                          |        | П  |   |          |                                |  |  |

|        | 6                                        | CA     | <u>1</u> | DEX           | MP                                               |            | × | П | П                          |        |    |   |          | POINT TO NEXT SCREEN           |  |  |

|        | 7                                        | Do     |          | BNE           | REL                                              | NEXTONAL   | П |   | П                          |        | П  |   |          | LOCATION - LAST CHARACTER ?    |  |  |

|        | 8                                        | EF     |          | $\overline{}$ |                                                  |            | П | П | П                          |        |    |   |          |                                |  |  |

|        | 9                                        | 60     |          | RTS           | IMP                                              |            | П |   |                            |        | П  |   |          | END AND RETURN FROM SUBBOUTINE |  |  |

|        | Α.                                       |        | i        |               |                                                  |            | П |   |                            |        |    |   |          |                                |  |  |

|        |                                          |        |          |               |                                                  |            | П |   |                            | $\neg$ |    |   |          | 1 100                          |  |  |

| $\neg$ | С                                        |        |          |               |                                                  |            | П |   |                            |        |    |   |          |                                |  |  |

|        | D                                        |        |          |               |                                                  |            | П |   | 1                          |        |    | 1 |          |                                |  |  |

|        | E                                        |        |          |               |                                                  |            | П |   | 7                          |        | ٦  | 7 |          |                                |  |  |

|        | F                                        |        |          |               |                                                  |            | П | ٦ |                            | ٦      | 1  | ٦ |          |                                |  |  |

Fig. 7 — Hand coded program of example routine (note this is the simplest though not necessarily the best way of writing this program).

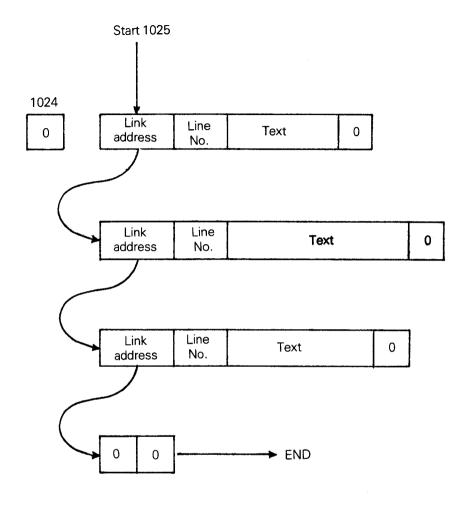

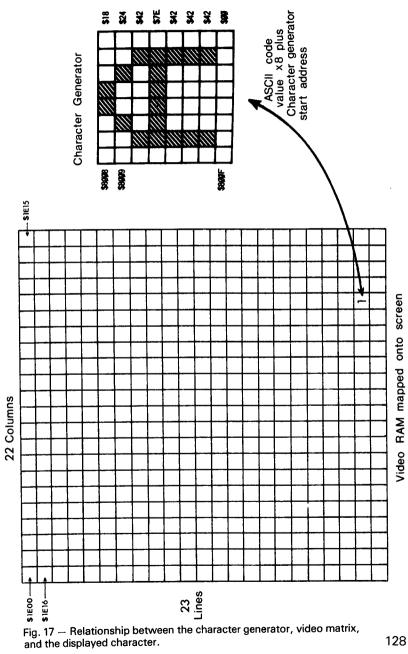

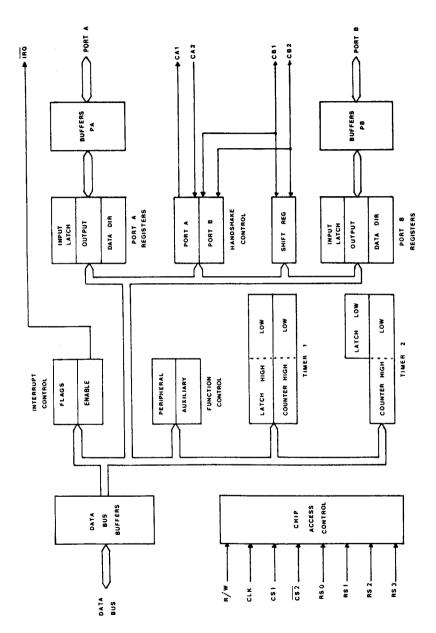

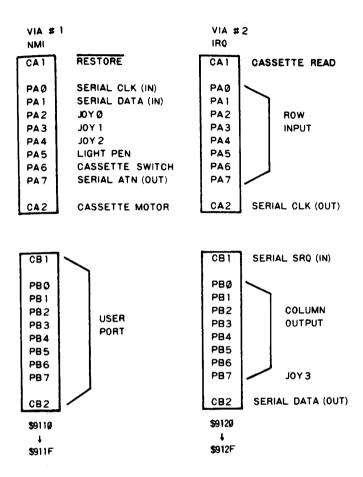

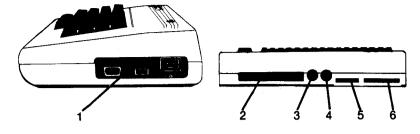

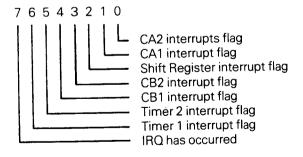

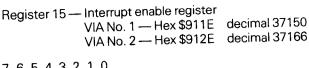

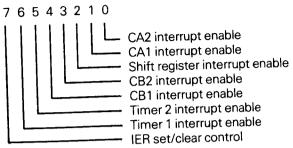

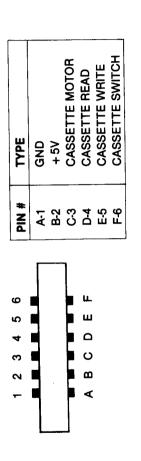

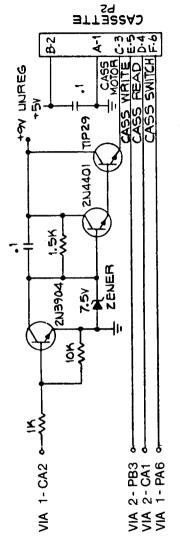

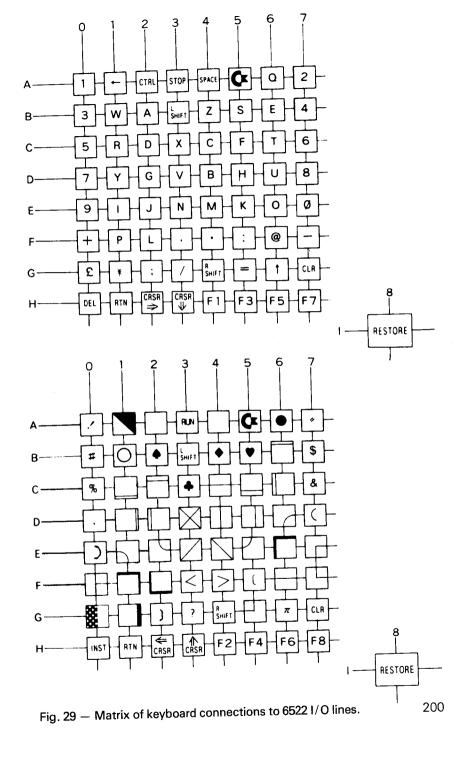

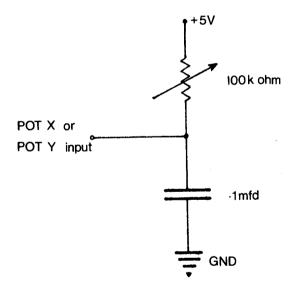

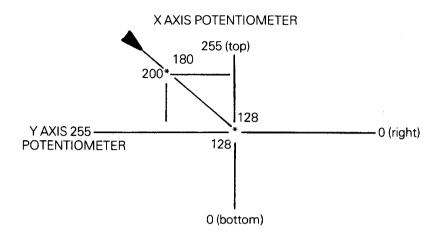

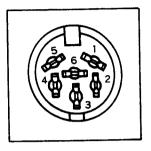

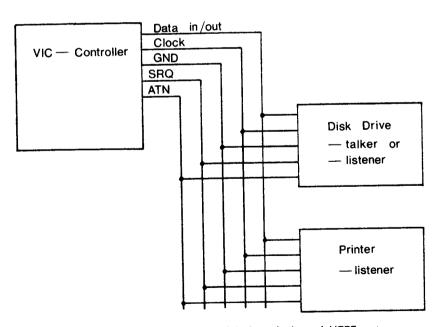

87 to 96 are best). If a larger section of page zero memory is required then the existing contents should be relocated to a protected part of memory before the machine code routine is run and restored at the end of the routine.